台积电第二代 3nm 工艺到来,N3E 芯片已流片

10 月 26 日消息,Alphawave 公司表示,其已经流片(Tape out)了业界首批使用台积电 N3E 制造技术(第二代 3 纳米级工艺节点)的芯片之一。该芯片已由台积电生产,并成功通过了所有必要的测试,将于本周晚些时候在台积电的 OIP 论坛上展示。

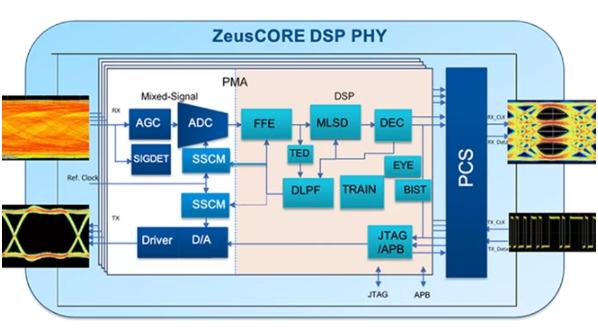

该芯片是 Alphawave IP ZeusCORE100 1-112Gbps NRZ / PAM4 串行器-解串器(SerDes),支持未来几年将流行的众多标准,包括 800G 以太网、OIF 112G-CEI、PCIe 6.0 和 CXL3.0。据称,SerDes 支持超长的通道,为下一代服务器提供灵活的连接解决方案。

Alphawave IP

Alphawave 公司总裁兼首席执行官 Tony Pialis 称:“Alphawave 很荣幸成为首批利用台积电最先进的 3 纳米技术的公司之一。我们的合作关系将继续带来创新的高速连接技术,为最先进的数据中心提供动力,我们很高兴能在台积电 OIP 论坛活动中展示这些解决方案。”

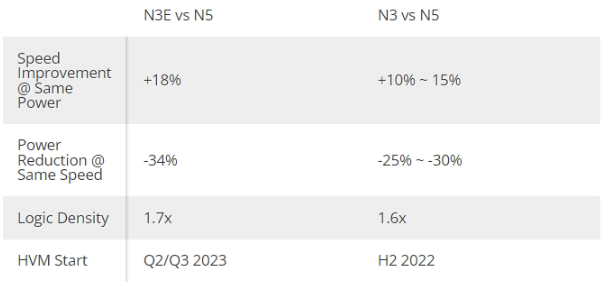

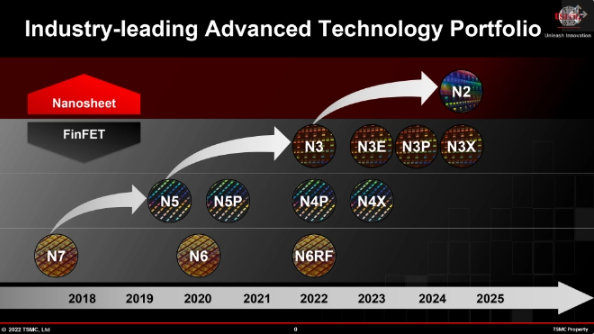

台积电计划在未来两到三年内推出五种 3 纳米级工艺技术,第一代 3nm 工艺 N3 预计将被台积电的大客户苹果用于少数设计,而第二代 3nm 工艺 N3E 将具有改进的工艺窗口,这意味着有更快的产出时间,更高的产量,更高的性能和更低的功耗。

N3E 预计将比 N3 更广泛地被采用,但其大规模生产计划在 2023 年中期或 2023 年第三季度开始,大约在台积电使用其 N3 生产节点启动大批量制造(HVM)一年后。

IT之家了解到,在台积电明年开始 N3E HVM 之后,其计划再提供三个 3 纳米级节点,包括面向性能的 N3P,用于需要高晶体管密度的芯片的 N3S,以及用于性能要求高的应用的 N3X,如微处理器。

相关文章

- 中国车企在新能源汽车领域领先 德国媒体发出警报

- 专家指责网约车成为北京拥堵的主要原因

- 巴菲特最初以2.32亿美元价格购买比亚迪2.25亿股股票 持股比例曾超过21%

- “新基石研究员项目”第二期启动,50位杰出科学家将获资助

- 国家邮政局发布2022年快递服务满意度调查结果,顺丰速运、京东快递、邮政速递获高分

- 中国汽车零部件制造商面临海外压力 要求在越南和印尼等国家建厂

- Twitter并入X Corp.公司引发热议 马斯克的计划揭开神秘面纱

- 阿里云核心产品全面Serverless化 性价比提升25%-60%

- 马斯克计划将Twitter打造成类似微信的超级应用程序

- 阿里云宣布开放通义千问的能力,帮助企业打造专属大模型

- 我国算力产业增速持续快速,规模居全球第二

- 小米高端化战略成效显著,近期新品好评率高达99%

- 吉林大学与高能时代新能源合作开发手机固态电池

- 移动支付公司Square致力于吸引高端客户

- 周杰伦起诉网易不正当竞争

- B站停止维护UWP版客户端,推荐下载桌面端

系统下载排行榜71011xp

番茄花园Win7 64位推荐旗舰版 V2021.05

2深度技术Win7 64位豪华旗舰版 V2021.07

3番茄花园Win7 64位旗舰激活版 V2021.07

4带USB3.0驱动Win7镜像 V2021

5系统之家 Ghost Win7 64位 旗舰激活版 V2021.11

6萝卜家园Win7 64位旗舰纯净版 V2021.08

7技术员联盟Win7 64位旗舰激活版 V2021.09

8雨林木风Win7 SP1 64位旗舰版 V2021.05

9萝卜家园Ghost Win7 64位极速装机版 V2021.04

10技术员联盟Win7 64位完美装机版 V2021.04

深度技术Win10 64位优化专业版 V2021.06

2深度技术Win10系统 最新精简版 V2021.09

3Win10超级精简版 V2021

4Win10完整版原版镜像 V2021

5风林火山Win10 21H1 64位专业版 V2021.06

6Win10光盘镜像文件 V2021

7深度技术 Ghost Win10 64位 专业稳定版 V2021.11

8技术员联盟Ghost Win10 64位正式版 V2021.10

9Win10 21H1 Build 19043.1320 官方正式版

10技术员联盟Win10 64位永久激活版镜像 V2021.07

系统之家 Ghost Win11 64位 官方正式版 V2021.11

2Win11PE网络纯净版 V2021

3系统之家Ghost Win11 64位专业版 V2021.10

4Win11官网纯净版 V2021.10

5Win11 RTM版镜像 V2021

6番茄花园Win11系统64位 V2021.09 极速专业版

7Win11专业版原版镜像ISO V2021

8Win11官方中文正式版 V2021

9Win11 22494.1000预览版 V2021.11

10番茄花园Win11 64位极速优化版 V2021.08

深度技术Windows XP SP3 稳定专业版 V2021.08

2雨林木风Ghost XP Sp3纯净版 V2021.08

3萝卜家园WindowsXP Sp3专业版 V2021.06

4雨林木风WindowsXP Sp3专业版 V2021.06

5风林火山Ghost XP Sp3纯净版 V2021.08

6技术员联盟Windows XP SP3极速专业版 V2021.07

7萝卜家园 Windows Sp3 XP 经典版 V2021.04

8番茄花园WindowsXP Sp3专业版 V2021.05

9电脑公司WindowsXP Sp3专业版 V2021.05

10番茄花园 GHOST XP SP3 纯净专业版 V2021.03

热门教程 更多+

装机必备 更多+

重装教程 更多+

电脑教程专题 更多+